#### TLV314, TLV2314, TLV4314

ZHCSEU4A -MARCH 2016-REVISED MARCH 2016

# TLVx314 3MHz、低功耗、 内部 EMI 滤波器、RRIO 运算放大器

### 1 特性

- 低偏移电压: 0.75mV (典型值)

- 低输入偏置电流: 1pA (典型值)

- 宽电源电压范围: 1.8V 至 5.5V

- 轨到轨输入和输出

- 增益带宽: 3MHz

- 低 Io: 250µA/通道(最大值)

- 低噪声: 1kHz 时为 16nV/√Hz

- 内部射频 (RF) / 电磁干扰 (EMI) 滤波器

- 扩展温度范围: -40°C 至 +125°C

## 2 应用范围

- 白色家电

- 手持测试设备

- 便携式血糖仪

- 远程感测

- 有源滤波器

- 工业自动化

- 电池供电型电子产品

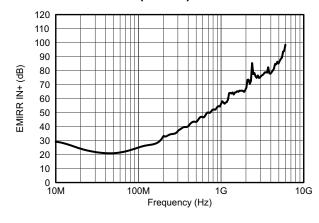

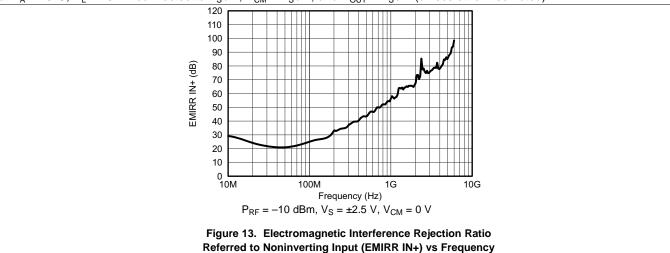

## 电磁干扰抑制比 (EMIRR) 与频率间的关系

### 3 说明

TLV314 系列单通道、双通道和四通道运算放大器代表了新一代的低功耗、通用运算放大器。该系列器件具有轨到轨输入和输出摆幅 (RRIO)、低静态电流(5V 时的典型值为 150μA/通道)以及 3MHz 的高带宽等特性,非常适用于 需要在成本与性能之间实现平衡 的应用。此外,TLV314 系列架构可实现低至 1pA 的输入偏置电流,因此适用于 源阻抗高达兆欧级的 应用。

TLV314 器件采用稳健耐用的设计,方便电路设计人员使用:单位增益稳定,具有 RRIO 和集成的 RF/EMI抑制滤波器,容性负载最高达 300 pF,在过驱情况下不出现反相,并且带有高静电放电 (ESD) 保护(4kV HBM)。

此类器件经过优化,适合在 1.8V ( $\pm 0.9V$ ) 至 5.5V ( $\pm 2.75V$ ) 的低电压状态下工作并可在  $-40^{\circ}C$  至  $+125^{\circ}C$  的扩展工业温度范围内额定运行。

TLV314(单通道)采用 5 引脚 SC70 和小外形尺寸晶体管 (SOT)-23 封装。TLV2314(双通道)采用 8 引脚小外形尺寸集成电路 (SOIC)和超薄小外形尺寸 (VSSOP)封装。四通道 TLV4314 采用 14 引脚薄型小外形尺寸 (TSSOP)封装。

#### 器件信息(1)

| 器件型号       | 封装         | 封装尺寸 (标称值)      |

|------------|------------|-----------------|

| TLV314     | SOT-23 (5) | 2.90mm x 1.60mm |

| 127314     | SC70 (5)   | 2.00mm × 1.25mm |

| TL \/224.4 | VSSOP (8)  | 3.00mm × 3.00mm |

| TLV2314    | SOIC (8)   | 4.90mm x 3.91mm |

| TLV4314    | TSSOP (14) | 5.00mm x 4.40mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

|   | 目表                                   | 录  |                                |           |

|---|--------------------------------------|----|--------------------------------|-----------|

| 1 | 特性1                                  |    | 8.4 Device Functional Modes    | 15        |

| 2 | 应用范围1                                | 9  | Application and Implementation | 16        |

| 3 | 说明1                                  |    | 9.1 Application Information    | 16        |

| 4 | 修订历史记录 2                             |    | 9.2 Typical Application        | 16        |

| 5 | Device Comparison Table 3            |    | 9.3 System Examples            | 17        |

| 6 | Pin Configuration and Functions      | 10 | Power Supply Recommendations   | 18        |

| 7 | Specifications                       |    | 10.1 Input and ESD Protection  | 18        |

| • | 7.1 Absolute Maximum Ratings         | 11 | Layout                         | 19        |

|   | 7.2 ESD Ratings                      |    | 11.1 Layout Guidelines         | 19        |

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example            | 19        |

|   | 7.4 Thermal Information: TLV314      | 12 | 器件和文档支持                        | 20        |

|   | 7.5 Thermal Information: TLV2314     |    | 12.1 器件支持                      | 20        |

|   | 7.6 Thermal Information: TLV43147    |    | 12.2 文档支持                      | <u>20</u> |

|   | 7.7 Electrical Characteristics 8     |    | 12.3 相关链接                      | 20        |

|   | 7.8 Typical Characteristics9         |    | 12.4 社区资源                      | 20        |

|   | 7.9 Typical Characteristics          |    | 12.5 商标                        |           |

| 8 | Detailed Description 13              |    | 12.6 静电放电警告                    |           |

|   | 8.1 Overview                         |    | 12.7 Glossary                  |           |

|   | 8.2 Functional Block Diagram         | 13 | 机械、封装和可订购信息                    | 20        |

|   | 8.3 Feature Description              |    |                                |           |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| CI | hanges from Original (March 2016) to Revision A | Page |

|----|-------------------------------------------------|------|

| •  | 已发布为量产数据                                        | 1    |

## 5 Device Comparison Table

|         | NO. OF   |        |      |      |       |       |

|---------|----------|--------|------|------|-------|-------|

| DEVICE  | CHANNELS | SOT-23 | SC70 | SOIC | VSSOP | TSSOP |

| TLV314  | 1        | 5      | 5    | _    | _     | _     |

| TLV2314 | 2        | _      | _    | 8    | 8     | _     |

| TLV4314 | 4        | _      | _    | _    | _     | 14    |

# 6 Pin Configuration and Functions

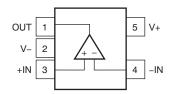

DBV Package: TLV314 5-Pin SOT-23 Top View

#### DCK Package: TLV314 5-Pin SC70 Top View

### Pin Functions: TLV314

| PIN  |     | PIN |     |                           |  |

|------|-----|-----|-----|---------------------------|--|

| NAME |     | NO. | 1/0 | DESCRIPTION               |  |

|      | DBV | DCK | _   |                           |  |

| -IN  | 4   | 3   | I   | Inverting input           |  |

| +IN  | 3   | 1   | I   | Noninverting input        |  |

| OUT  | 1   | 4   | 0   | Output                    |  |

| V-   | 2   | 2   | _   | Negative (lowest) supply  |  |

| V+   | 5   | 5   | _   | Positive (highest) supply |  |

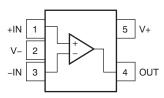

## D, DGK Package: TLV2314 8-Pin SOIC or VSSOP Top View

## Pin Functions: TLV2314

| PIN   |     | 1/0 | DESCRIPTION                   |  |

|-------|-----|-----|-------------------------------|--|

| NAME  | NO. | 1/0 | DESCRIPTION                   |  |

| −IN A | 2   | I   | nverting input, channel A     |  |

| +IN A | 3   | I   | oninverting input, channel A  |  |

| –IN B | 6   | I   | nverting input, channel B     |  |

| +IN B | 5   | I   | Noninverting input, channel B |  |

| OUT A | 1   | 0   | Output, channel A             |  |

| OUT B | 7   | 0   | Output, channel B             |  |

| V-    | 4   | _   | Negative (lowest) supply      |  |

| V+    | 8   | _   | Positive (highest) supply     |  |

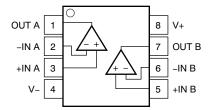

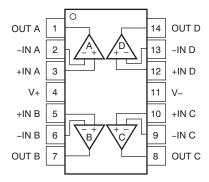

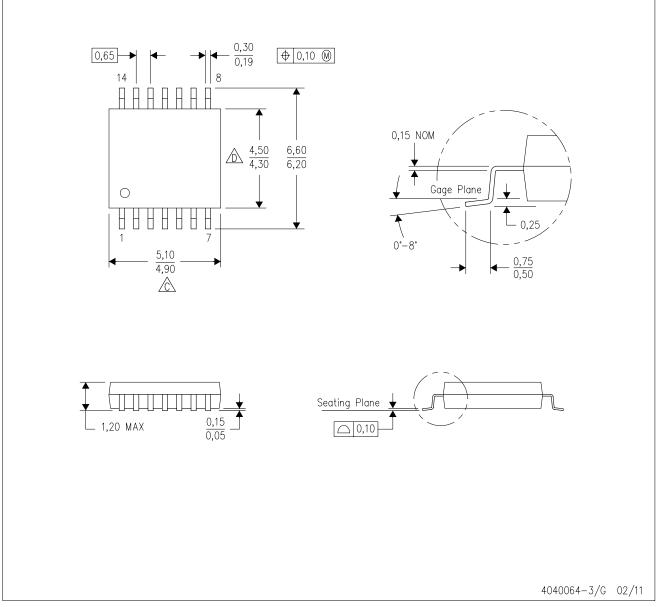

#### PW Package: TLV4314 14-Pin TSSOP Top View

### Pin Functions: TLV4314

|       | PIN I/O |     | DECCRIPTION                   |  |

|-------|---------|-----|-------------------------------|--|

| NAME  | NO.     | 1/0 | DESCRIPTION                   |  |

| –IN A | 2       | I   | Inverting input, channel A    |  |

| +IN A | 3       | I   | ninverting input, channel A   |  |

| –IN B | 6       | I   | rting input, channel B        |  |

| +IN B | 5       | I   | Noninverting input, channel B |  |

| –IN C | 9       | I   | rting input, channel C        |  |

| +IN C | 10      | I   | Noninverting input, channel C |  |

| –IN D | 13      | I   | Inverting input, channel D    |  |

| +IN D | 12      | I   | Noninverting input, channel D |  |

| OUT A | 1       | 0   | Output, channel A             |  |

| OUT B | 7       | 0   | Output, channel B             |  |

| OUT C | 8       | 0   | Output, channel C             |  |

| OUT D | 14      | 0   | Output, channel D             |  |

| V-    | 11      | _   | Negative (lowest) supply      |  |

| V+    | 4       | _   | Positive (highest) supply     |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                          |                           | MIN        | MAX        | UNIT |

|--------------------------|---------------------------|------------|------------|------|

| Supply voltage           |                           |            | 7          | V    |

| Cinnal innut nina        | Voltage (2)               | (V-) - 0.5 | (V+) + 0.5 | V    |

| Signal input pins        | Current <sup>(2)</sup>    | -10        | 10         | mA   |

| Output short-circuit (3) |                           | Con        | inuous     | mA   |

|                          | Specified, T <sub>A</sub> | -40        | 125        |      |

| Temperature              | Junction, T <sub>J</sub>  |            | 150        | °C   |

|                          | Storage, T <sub>stg</sub> | -65        | 150        |      |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

### 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Clastrostatia disabarga | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                               |                             |               | MIN   | NOM MAX | UNIT |

|-------------------------------|-----------------------------|---------------|-------|---------|------|

| V                             | Cumply valtage              | Single supply | 1.8   | 5.5     | \/   |

| V <sub>S</sub> Supply voltage | Dual supply                 | ±0.9          | ±2.75 | V       |      |

|                               | Specified temperature range |               | -40   | 125     | °C   |

<sup>(2)</sup> Input pins are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5 V beyond the supply rails must be current limited to 10 mA or less.

<sup>(3)</sup> Short-circuit to ground, one amplifier per package.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information: TLV314

|                      |                                              | 1            | LV314      |      |

|----------------------|----------------------------------------------|--------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | DCK (SC70) | UNIT |

|                      |                                              | 5 PINS       | 5 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 228.5        | 281.4      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case(top) thermal resistance     | 99.1         | 91.6       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 54.6         | 59.6       | °C/W |

| $\psi_{JT}$          | Junction-to-top characterization parameter   | 7.7          | 1.5        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 53.8         | 58.8       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report. SPRA953.

### 7.5 Thermal Information: TLV2314

|                       |                                              | TL       | TLV2314     |      |  |  |

|-----------------------|----------------------------------------------|----------|-------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | DGK (VSSOP) | UNIT |  |  |

|                       |                                              | 8 PINS   | 8 PINS      |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 138.4    | 191.2       | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case(top) thermal resistance     | 89.5     | 61.9        | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 78.6     | 111.9       | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 29.9     | 5.1         | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 78.1     | 110.2       | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.6 Thermal Information: TLV4314

|                      |                                              | TLV      | TLV4314    |      |  |  |

|----------------------|----------------------------------------------|----------|------------|------|--|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | PW (TSSOP) | UNIT |  |  |

|                      |                                              | 14 PINS  | 14 PINS    |      |  |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 93.2     | 121        | °C/W |  |  |

| $R_{\theta JC(top)}$ | Junction-to-case(top) thermal resistance     | 51.8     | 49.4       | °C/W |  |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 49.4     | 62.8       | °C/W |  |  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 13.5     | 5.9        | °C/W |  |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 42.2     | 62.2       | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 7.7 Electrical Characteristics

1.8 \/ to 5.5 \/: at T.

|                      | PARAMETE                                          | R                   | TEST CONDITIONS                                                                                                                                 | MIN TY     | P MAX      | UNIT         |

|----------------------|---------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|

| OFFSET               | VOLTAGE                                           |                     |                                                                                                                                                 |            |            |              |

| V <sub>os</sub>      | Input offset voltage                              |                     | V <sub>CM</sub> = (V <sub>S</sub> +) - 1.3 V, T <sub>A</sub> = 25°C                                                                             | ±0.7       | '5 ±3      | mV           |

| dV <sub>OS</sub> /dT | V <sub>OS</sub> vs temperature                    |                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                                            |            | 2          | μV/°C        |

| PSRR                 | Power-supply rejecti                              | on ratio            | V <sub>CM</sub> = (V <sub>S</sub> +) - 1.3 V, T <sub>A</sub> = 25°C                                                                             | ±í         | 0 ±135     | μV/V         |

|                      | Channel separation,                               | dc                  | At dc, $T_A = 25$ °C                                                                                                                            | 10         | 10         | dB           |

| INPUT V              | OLTAGE RANGE                                      |                     |                                                                                                                                                 |            |            |              |

| V <sub>CM</sub>      | Common-mode volta                                 | age range           | T <sub>A</sub> = 25°C                                                                                                                           | (V-) - 0.2 | (V+) + 0.2 | V            |

| CMRR                 | Common-mode rejection ratio                       |                     | $V_S = 5.5 \text{ V}, (V_{S}-) - 0.2 \text{ V} < V_{CM} < (V_{S}+) - 1.3 \text{ V}, $ $T_A = 25^{\circ}\text{C}$                                |            | 06         | dB           |

|                      |                                                   |                     | $V_S = 5.5 \text{ V}, V_{CM} = -0.2 \text{ V to } 5.7 \text{ V}^{(2)}, T_A = 25^{\circ}\text{C}$                                                | -          | 75         |              |

| INPUT B              | IAS CURRENT                                       |                     |                                                                                                                                                 |            |            |              |

| I <sub>B</sub>       | Input bias current                                |                     | T <sub>A</sub> = 25°C                                                                                                                           | ±1         | .0         | pА           |

| Ios                  | Input offset current                              |                     | T <sub>A</sub> = 25°C                                                                                                                           | ±1         | .0         | pА           |

| NOISE                | •                                                 |                     |                                                                                                                                                 |            |            | -            |

|                      | Input voltage noise (                             | peak-to-peak)       | f = 0.1 Hz to 10 Hz, T <sub>A</sub> = 25°C                                                                                                      |            | 5          | $\mu V_{PP}$ |

|                      |                                                   |                     | f = 10 kHz, T <sub>A</sub> = 25°C                                                                                                               | ,          | 5          |              |

| e <sub>n</sub>       | Input voltage noise                               | density             | f = 1 kHz, T <sub>A</sub> = 25°C                                                                                                                |            | 6          | nV/√Hz       |

| i <sub>n</sub>       | Input current noise of                            | lensity             | f = 1 kHz, T <sub>A</sub> = 25°C                                                                                                                |            | 6          | fA/√Hz       |

|                      | APACITANCE                                        |                     | , N                                                                                                                                             |            |            |              |

|                      |                                                   | Differential        | V <sub>S</sub> = 5 V, T <sub>A</sub> = 25°C                                                                                                     |            | 1          |              |

| C <sub>IN</sub>      | Input capacitance                                 | Common-mode         | $V_S = 5 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                                                   |            | 5          | pF           |

| OPEN-LO              | OOP GAIN                                          |                     | 13 0 1, 1 <sub>A</sub> =0 0                                                                                                                     |            | <u>-</u>   |              |

|                      | Open-loop voltage gain                            |                     | $V_S = 1.8 \text{ V to } 5.5 \text{ V}, 0.2 \text{ V} < V_O < (V+) - 0.2 \text{ V}, \\ R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$      | 85 11      | 5          |              |

| A <sub>OL</sub>      |                                                   |                     | $V_S = 1.8 \text{ V to } 5.5 \text{ V}, 0.5 \text{ V} < V_O < (V+) - 0.5 \text{ V}, \\ R_L = 2 \text{ k}\Omega^{(2)}, T_A = 25^{\circ}\text{C}$ | 85 10      | 0          | dB           |

|                      | Phase margin                                      |                     | $V_S = 5 \text{ V}, \text{ G} = 1, \text{ R}_L = 10 \text{ k}\Omega, \text{ T}_A = 25^{\circ}\text{C}$                                          | 6          | 55         | ٥            |

| FREQUE               | ENCY RESPONSE                                     |                     |                                                                                                                                                 |            |            |              |

|                      |                                                   |                     | $V_S = 1.8 \text{ V}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, T_A = 25^{\circ}\text{C}$                                                  | 2          | .7         |              |

| GBW                  | Gain-bandwidth prod                               | duct                | $V_S = 5 \text{ V}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, T_A = 25^{\circ}\text{C}$                                                    |            | 3          | MHz          |

| SR                   | Slew rate <sup>(3)</sup>                          |                     | V <sub>S</sub> = 5 V, G = 1, T <sub>A</sub> = 25°C                                                                                              | 1          | 1.5        |              |

| t <sub>S</sub>       | Settling time                                     |                     | To 0.1%, V <sub>S</sub> = 5 V, 2-V step , G = 1, T <sub>A</sub> = 25°C                                                                          |            | 3          | μs           |

|                      | Overload recovery ti                              | me                  | $V_S = 5 \text{ V}, V_{IN} \times \text{gain} > V_S, T_A = 25^{\circ}\text{C}$                                                                  |            | 8          | μs           |

| THD+N                | Total harmonic disto                              |                     | $V_S = 5 \text{ V}, V_O = 1 \text{ V}_{RMS}, G = 1, f = 1 \text{ kHz},$ $R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                    | 0.005      | %          |              |

| OUTPUT               | Ī                                                 |                     |                                                                                                                                                 | *          |            |              |

|                      |                                                   |                     | $V_S = 1.8 \text{ V to } 5.5 \text{ V}, R_L = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                                     |            | 5 25       |              |

| Vo                   | Voltage output swing                              | g from supply rails | $V_S = 1.8 \text{ V to } 5.5 \text{ V}, R_L = 2 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                                      | 2          | 2 45       | mV           |

| I <sub>SC</sub>      | Short-circuit current                             |                     | V <sub>S</sub> = 5 V, T <sub>A</sub> = 25°C                                                                                                     | ±2         |            | mA           |

| R <sub>O</sub>       | Open-loop output impedance                        |                     | V <sub>S</sub> = 5.5 V, f = 100 Hz, T <sub>A</sub> = 25°C                                                                                       | 57         |            | Ω            |

|                      | SUPPLY                                            | •                   | 1                                                                                                                                               |            |            | 1            |

| V <sub>S</sub>       | Specified voltage rai                             | nge                 |                                                                                                                                                 | 1.8        | 5.5        | V            |

| I <sub>Q</sub>       | Quiescent current per amplifier, over temperature |                     | $V_S = 5 \text{ V}, I_O = 0 \text{ mA}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                     | 15         |            | μA           |

|                      |                                                   |                     |                                                                                                                                                 |            |            |              |

| TEMPER               | (AIURE                                            |                     |                                                                                                                                                 |            |            |              |

| TEMPER               | Specified range                                   |                     |                                                                                                                                                 | -40        | 125        | °C           |

<sup>(1)</sup> Parameters with minimum or maximum specification limits are 100% production tested at 25°C, unless otherwise noted. Overtemperature limits are based on characterization and statistical analysis.

Specified by design and characterization; not production tested.

Signifies the slower value of the positive or negative slew rate. Third-order filter; bandwidth = 80 kHz at -3 dB.

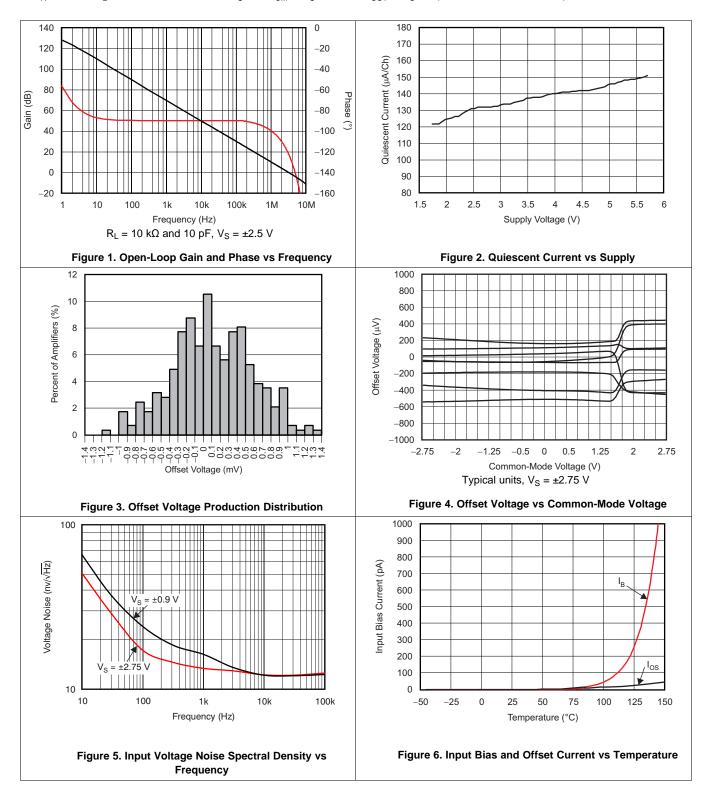

## 7.8 Typical Characteristics

# Table 1. Table of Graphs

| TITLE                                                            | FIGURE    |

|------------------------------------------------------------------|-----------|

| Open-Loop Gain and Phase vs Frequency                            | Figure 1  |

| Quiescent Current vs Supply Voltage                              | Figure 2  |

| Offset Voltage Production Distribution                           | Figure 3  |

| Offset Voltage vs Common-Mode Voltage (Maximum Supply)           | Figure 4  |

| Input Voltage Noise Spectral Density vs Frequency (1.8 V, 5.5 V) | Figure 5  |

| Input Bias and Offset Current vs Temperature                     | Figure 6  |

| Output Voltage Swing vs Output Current (over Temperature)        | Figure 7  |

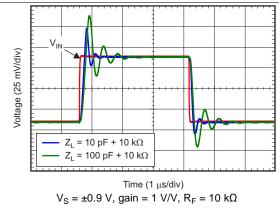

| Small-Signal Overshoot vs Load Capacitance                       | Figure 8  |

| Small-Signal Step Response, Noninverting (1.8 V)                 | Figure 9  |

| Large-Signal Step Response, Noninverting (1.8 V)                 | Figure 10 |

| No Phase Reversal                                                | Figure 11 |

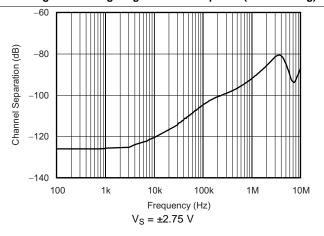

| Channel Separation vs Frequency (Dual)                           | Figure 12 |

| EMIRR                                                            | Figure 13 |

### TEXAS INSTRUMENTS

## 7.9 Typical Characteristics

at  $T_A = 25^{\circ}C$ ,  $R_L = 10~k\Omega$  connected to  $V_S$  / 2,  $V_{CM} = V_S$  / 2, and  $V_{OUT} = V_S$  / 2 (unless otherwise noted)

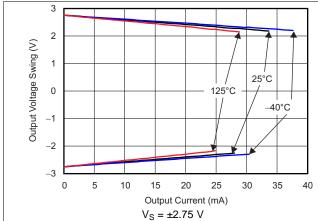

## **Typical Characteristics (continued)**

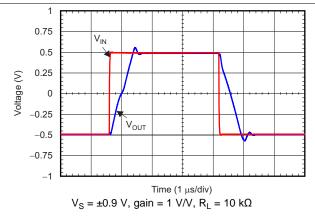

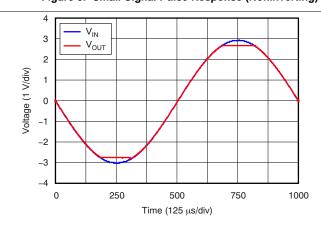

at  $T_A = 25$ °C,  $R_L = 10$  k $\Omega$  connected to  $V_S$  / 2,  $V_{CM} = V_S$  / 2, and  $V_{OUT} = V_S$  / 2 (unless otherwise noted)

Figure 7. Output Voltage Swing vs Output Current (Over Temperature)

Figure 8. Small-Signal Overshoot vs Load Capacitance

Figure 9. Small-Signal Pulse Response (Noninverting)

Figure 10. Large-Signal Pulse Response (Noninverting)

Figure 11. No Phase Reversal

Figure 12. Channel Separation vs Frequency (TLV2314)

## **Typical Characteristics (continued)**

at  $T_A = 25$ °C,  $R_L = 10$  k $\Omega$  connected to  $V_S$  / 2,  $V_{CM} = V_S$  / 2, and  $V_{OUT} = V_S$  / 2 (unless otherwise noted)

## 8 Detailed Description

#### 8.1 Overview

The TLV314 is a family of low-power, rail-to-rail input and output operational amplifiers specifically designed for portable applications. These devices operate from 1.8 V to 5.5 V, are unity-gain stable, and suitable for a wide range of general-purpose applications. The class AB output stage is capable of driving  $\leq$  10-k $\Omega$  loads connected to any point between V+ and ground. The input common-mode voltage range includes both rails, and allows the TLV314 series to be used in virtually any single-supply application. Rail-to-rail input and output swing significantly increases dynamic range, especially in low-supply applications, and makes these devices ideal for driving sampling analog-to-digital converters (ADCs).

The TLV314 features 3-MHz bandwidth and 1.5-V/ $\mu$ s slew rate with only 150- $\mu$ A supply current per channel, providing good ac performance at very low power consumption. DC applications are also well served with a very low input noise voltage of 14 nV/ $\sqrt{Hz}$  at 1 kHz, low input bias current (0.2 pA), and an input offset voltage of 0.5 mV (typical).

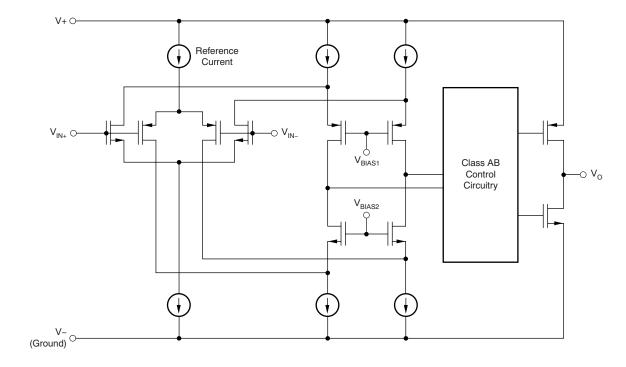

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Operating Voltage

The TLV314 series of operational amplifiers is fully specified and ensured for operation from 1.8 V to 5.5 V. In addition, many specifications apply from –40°C to +125°C. Parameters that vary significantly with operating voltages or temperature are provided in the *Typical Characteristics* section. Bypass power-supply pins with 0.01-µF ceramic capacitors.

#### 8.3.2 Rail-to-Rail Input

The input common-mode voltage range of the TLV314 series extends 200 mV beyond the supply rails. This performance is achieved with a complementary input stage: an N-channel input differential pair in parallel with a P-channel differential pair; see the *Functional Block Diagram* section. The N-channel pair is active for input voltages close to the positive rail, typically (V+) - 1.3 V to 200 mV above the positive supply, and the P-channel pair is on for inputs from 200 mV below the negative supply to approximately (V+) - 1.3 V. There is a small transition region, typically (V+) - 1.4 V to (V+) - 1.2 V, in which both pairs are on. This 200-mV transition region can vary up to 300 mV with process variation. Thus, the transition region (both stages on) can range from (V+) - 1.7 V to (V+) - 1.5 V on the low end, up to (V+) - 1.1 V to (V+) - 0.9 V on the high end. Within this transition region, PSRR, CMRR, offset voltage, offset drift, and THD can be degraded compared to device operation outside this region.

#### 8.3.3 Rail-to-Rail Output

Designed as a micro-power, low-noise operational amplifier, the TLV314 delivers a robust output drive capability. A class AB output stage with common-source transistors is used to achieve full rail-to-rail output swing capability. For resistive loads up to 10 k $\Omega$ , the output typically swings to within 5 mV of either supply rail regardless of the power-supply voltage applied. Different load conditions change the ability of the amplifier to swing close to the rails; see Figure 7.

#### 8.3.4 Common-Mode Rejection Ratio (CMRR)

The CMRR for the TLV314 is specified in several ways so the best match for a given application can be used; see the *Electrical Characteristics* table. First, the CMRR of the device in the common-mode range below the transition region  $[V_{CM} < (V+) - 1.3 \text{ V}]$  is given. This specification is the best indicator of the capability of the device when the application requires using one of the differential input pairs. Second, the CMRR over the entire common-mode range is specified at  $(V_{CM} = -0.2 \text{ V} \text{ to } 5.7 \text{ V})$ . This last value includes the variations measured through the transition region (see Figure 4).

#### **Feature Description (continued)**

#### 8.3.5 Capacitive Load and Stability

The TLV314 is designed to be used in applications where driving a capacitive load is required. As with all operational amplifiers, there may be specific instances where the TLV314 can become unstable. The particular operational amplifier circuit configuration, layout, gain, and output loading are some of the factors to consider when establishing whether or not an amplifier is stable in operation. An operational amplifier in the unity-gain (1 V/V) buffer configuration that drives a capacitive load exhibits a greater tendency to be unstable than an amplifier operated at a higher noise gain. The capacitive load, in conjunction with the operational amplifier output resistance, creates a pole within the feedback loop that degrades the phase margin. The degradation of the phase margin increases when capacitive loading increases. When operating in the unity-gain configuration, the TLV314 remains stable with a pure capacitive load up to approximately 1 nF. The equivalent series resistance (ESR) of some very large capacitors ( $C_L$  greater than 1  $\mu$ F) is sufficient to alter the phase characteristics in the feedback loop such that the amplifier remains stable. Increasing the amplifier closed-loop gain allows the amplifier to drive increasingly larger capacitance. This increased capability is evident when measuring the overshoot response of the amplifier at higher voltage gains; see Figure 8.

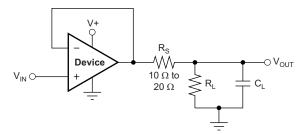

One technique for increasing the capacitive load drive capability of the amplifier operating in a unity-gain configuration is to insert a small resistor (typically 10  $\Omega$  to 20  $\Omega$ ) in series with the output, as shown in Figure 14. This resistor significantly reduces the overshoot and ringing associated with large capacitive loads. One possible problem with this technique, however, is that a voltage divider is created with the added series resistor and any resistor connected in parallel with the capacitive load. The voltage divider introduces a gain error at the output that reduces the output swing.

Figure 14. Improving Capacitive Load Drive

#### 8.3.6 EMI Susceptibility and Input Filtering

Operational amplifiers vary with regard to the susceptibility of the device to electromagnetic interference (EMI). If conducted EMI enters the operational amplifier, the dc offset observed at the amplifier output can shift from its nominal value when EMI is present. This shift is a result of signal rectification associated with the internal semiconductor junctions. Although all operational amplifier pin functions can be affected by EMI, the signal input pins are likely to be the most susceptible. The TLV314 operational amplifier family incorporates an internal input low-pass filter that reduces the amplifiers response to EMI. Both common-mode and differential mode filtering are provided by this filter. The filter is designed for a cutoff frequency of approximately 80 MHz (–3 dB), with a roll-off of 20 dB per decade.

Texas Instruments has developed the ability to accurately measure and quantify the immunity of an operational amplifier over a broad frequency spectrum extending from 10 MHz to 6 GHz. The EMI rejection ratio (EMIRR) metric allows operational amplifiers to be directly compared by the EMI immunity. Figure 13 illustrates the results of this testing on the TLV314. Detailed information can also be found in application report, *EMI Rejection Ratio of Operational Amplifiers* (SBOA128), available for download from www.ti.com.

#### 8.4 Device Functional Modes

The TLV314 family has a single functional mode. These devices are powered on as long as the power-supply voltage is between 1.8 V (±0.9 V) and 5.5 V (±2.75 V).

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TLV314 device is a low-power, rail-to-rail input and output operational amplifier specifically designed for portable applications. These devices operate from 1.8 V to 5.5 V, are unity-gain stable, and suitable for a wide range of general-purpose applications. The class AB output stage is capable of driving  $\leq$  10-k $\Omega$  loads connected to any point between V+ and ground. The input common-mode voltage range includes both rails, and allows the TLV314 device to be used in virtually any single-supply application. Rail-to-rail input and output swing significantly increases dynamic range, especially in low-supply applications, and makes the device ideal for driving sampling analog-to-digital converters (ADCs).

The TLV314 family of devices features a 3-MHz bandwidth and 1.5-V/ $\mu$ s slew rate with only 150- $\mu$ A supply current per channel, providing good ac performance at very low power consumption. DC applications are also well served with a very-low input noise voltage of 14 nV/ $\sqrt{Hz}$  at 1 kHz, low-input bias current (0.2 pA), and an input offset voltage of 0.5 mV (typical).

## 9.2 Typical Application

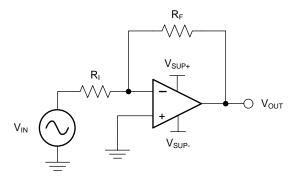

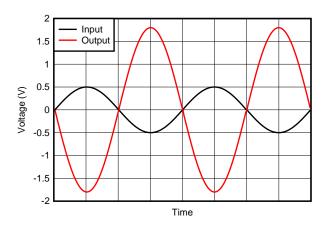

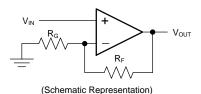

A typical application for an operational amplifier is an inverting amplifier, as shown in Figure 15. An inverting amplifier takes a positive voltage on the input and outputs a signal inverted to the input, making a negative voltage of the same magnitude. In the same manner, the amplifier also makes negative input voltages positive on the output. In addition, amplification can be added by selecting the input resistor R<sub>I</sub> and the feedback resistor R<sub>E</sub>.

Figure 15. Application Schematic

#### 9.2.1 Design Requirements

The supply voltage must be chosen to be larger than the input voltage range and the desired output range. The limits of the input common-mode range ( $V_{CM}$ ) and the output voltage swing to the rails ( $V_{O}$ ) must also be considered. For instance, this application scales a signal of  $\pm 0.5$  V (1 V) to  $\pm 1.8$  V (3.6 V). Setting the supply at  $\pm 2.5$  V is sufficient to accommodate this application.

### 9.2.2 Detailed Design Procedure

Determine the gain required by the inverting amplifier using Equation 1 and Equation 2:

$$A_{V} = \frac{V_{OUT}}{V_{IN}} \tag{1}$$

$$A_{V} = \frac{1.8}{-0.5} = -3.6 \tag{2}$$

#### **Typical Application (continued)**

When the desired gain is determined, choose a value for  $R_I$  or  $R_F$ . Choosing a value in the kilo ohm range is desirable for general-purpose applications because the amplifier circuit uses currents in the milliamp range. This milliamp current range ensures the device does not draw too much current. The trade-off is that very large resistors (100s of kilo ohms) draw the smallest current but generate the highest noise. Very small resistors (100s of ohms) generate low noise but draw high current. This example uses 10 k $\Omega$  for  $R_I$ , meaning 36 k $\Omega$  is used for  $R_F$ . These values are determined by Equation 3:

$$A_{V} = -\frac{R_{F}}{R_{I}} \tag{3}$$

### 9.2.3 Application Curve

Figure 16. Inverting Amplifier Input and Output

#### 9.3 System Examples

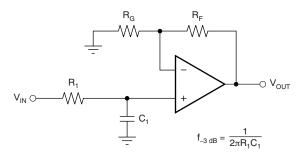

When receiving low-level signals, limiting the bandwidth of the incoming signals into the system is often required. The simplest way to establish this limited bandwidth is to place an RC filter at the noninverting terminal of the amplifier, as Figure 17 shows.

$$\frac{V_{OUT}}{V_{IN}} = \left(1 + \frac{R_F}{R_G}\right) \left(\frac{1}{1 + sR_1C_1}\right)$$

Figure 17. Single-Pole, Low-Pass Filter

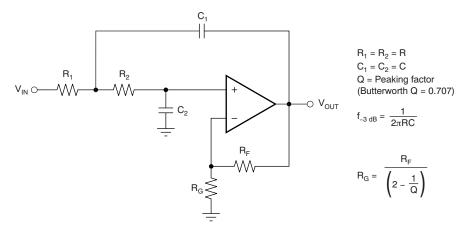

#### System Examples (continued)

If even more attenuation is needed, a multiple pole filter is required. The Sallen-Key filter can be used for this task, as Figure 18 shows. For best results, the amplifier must have a bandwidth that is eight to ten times the filter frequency bandwidth. Failure to follow this guideline can result in phase shift of the amplifier.

Figure 18. Two-Pole, Low-Pass, Sallen-Key Filter

## 10 Power Supply Recommendations

The TLV314 family is specified for operation from 1.8 V to 5.5 V (±0.9 V to ±2.75 V); many specifications apply from –40°C to +125°C. The *Typical Characteristics* section presents parameters that can exhibit significant variance with regard to operating voltage or temperature.

#### **CAUTION**

Supply voltages larger than 7 V can permanently damage the device (see the *Absolute Maximum Ratings* table).

Place 0.1-µF bypass capacitors close to the power-supply pins to reduce errors coupling in from noisy or high-impedance power supplies. For more detailed information on bypass capacitor placement; see the *Layout Guidelines* section.

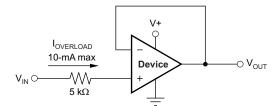

#### 10.1 Input and ESD Protection

The TLV314 family incorporates internal electrostatic discharge (ESD) protection circuits on all pins. In the case of input and output pins, this protection primarily consists of current-steering diodes connected between the input and power-supply pins. These ESD protection diodes also provide in-circuit, input overdrive protection, as long as the current is limited to 10 mA as stated in the *Absolute Maximum Ratings* table. Figure 19 shows how a series input resistor can be added to the driven input to limit the input current. The added resistor contributes thermal noise at the amplifier input, which must be kept to a minimum in noise-sensitive applications.

**Figure 19. Input Current Protection**

#### 11 Layout

#### 11.1 Layout Guidelines

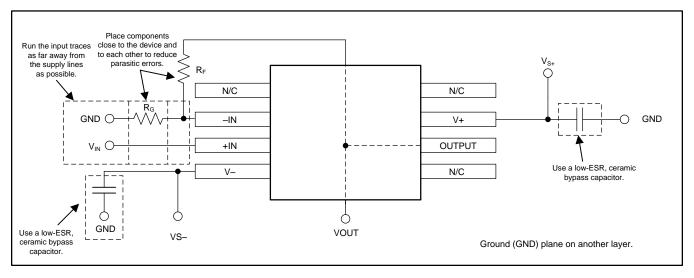

For best operational performance of the device, use good printed circuit board (PCB) layout practices, including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole and the

operational amplifier. Use bypass capacitors to reduce the coupled noise by providing low-impedance

power sources local to the analog circuitry.

- Connect low-ESR, 0.1-µF ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for singlesupply applications.

- Separate grounding for analog and digital portions of the circuitry is one of the simplest and most

effective methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to

ground planes. A ground plane helps distribute heat and reduces EMI noise pickup. Make sure to

physically separate digital and analog grounds, paying attention to the flow of the ground current. For

more detailed information, see Circuit Board Layout Techniques, SLOA089.

- To reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If these traces cannot be kept separate, crossing the sensitive trace perpendicularly is much better than crossing in parallel with the noisy trace.

- Place the external components as close to the device as possible. Keep R<sub>F</sub> and R<sub>G</sub> close to the inverting input in order to minimize parasitic capacitance, as shown in Figure 20.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

#### 11.2 Layout Example

Figure 20. Operational Amplifier Board Layout for Noninverting Configuration

#### 12 器件和文档支持

#### 12.1 器件支持

#### 12.2 文档支持

#### 12.2.1 相关文档

相关文档如下:

- 《运算放大器的电磁干扰 (EMI) 抑制比》, SBOA128

- 《电路板布局布线技巧》, SLOA089

- 《QFN/SON PCB 连接》, SLUA271

- 《四方扁平无引线逻辑器件封装》, SCBA017

#### 12.3 相关链接

表 2 列出了快速访问链接。范围包括技术文档、支持与社区资源、工具和软件,以及样片或购买的快速访问。

| ŧ. | 2  | 40 | 关链接 |

|----|----|----|-----|

| ᅏ  | Z. | ÆΠ | 大性技 |

| 器件      | 产品文件夹 | 样片与购买 | 技术文档  | 工具与软件 | 支持与社区 |

|---------|-------|-------|-------|-------|-------|

| TLV314  | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| TLV2314 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

| TLV4314 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 | 请单击此处 |

### 12.4 社区资源

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 12.5 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.6 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

## 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 13 机械、封装和可订购信息

以下页中包括机械、封装和可订购信息。这些信息是针对指定器件可提供的最新数据。这些数据会在无通知且不对本文档进行修订的情况下发生改变。欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

#### 重要声明

德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行 复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

|               |                                    |              |                          |

邮寄地址: 上海市浦东新区世纪大道1568 号,中建大厦32 楼邮政编码: 200122 Copyright © 2016, 德州仪器半导体技术(上海)有限公司

30-Mar-2016

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing |    | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|----|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| TLV2314IDGKR     | ACTIVE | VSSOP        | DGK                | 8  | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 13E7                 | Samples |

| TLV2314IDGKT     | ACTIVE | VSSOP        | DGK                | 8  | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAG      | Level-2-260C-1 YEAR | -40 to 125   | 13E7                 | Samples |

| TLV2314IDR       | ACTIVE | SOIC         | D                  | 8  | 2500           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | V2314                | Samples |

| TLV314IDBVR      | ACTIVE | SOT-23       | DBV                | 5  | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | 12H                  | Samples |

| TLV314IDBVT      | ACTIVE | SOT-23       | DBV                | 5  | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | 12H                  | Samples |

| TLV314IDCKR      | ACTIVE | SC70         | DCK                | 5  | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 121                  | Samples |

| TLV314IDCKT      | ACTIVE | SC70         | DCK                | 5  | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM  | -40 to 125   | 121                  | Samples |

| TLV4314IPWR      | ACTIVE | TSSOP        | PW                 | 14 | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | V4314                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

## PACKAGE OPTION ADDENDUM

30-Mar-2016

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

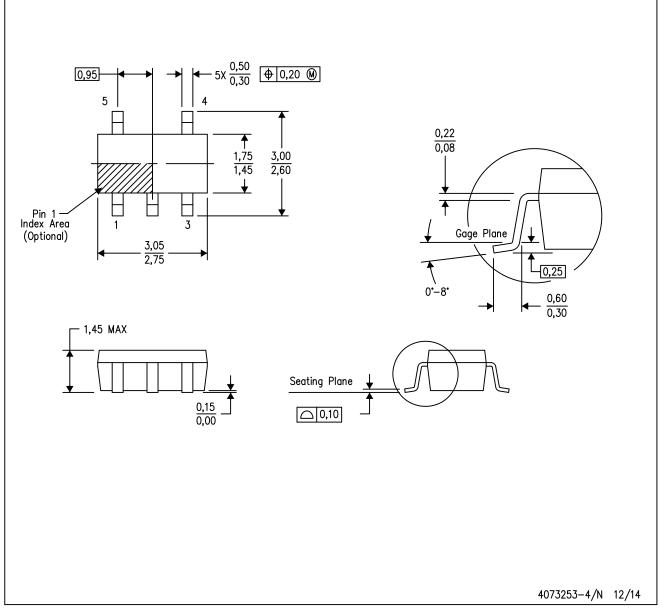

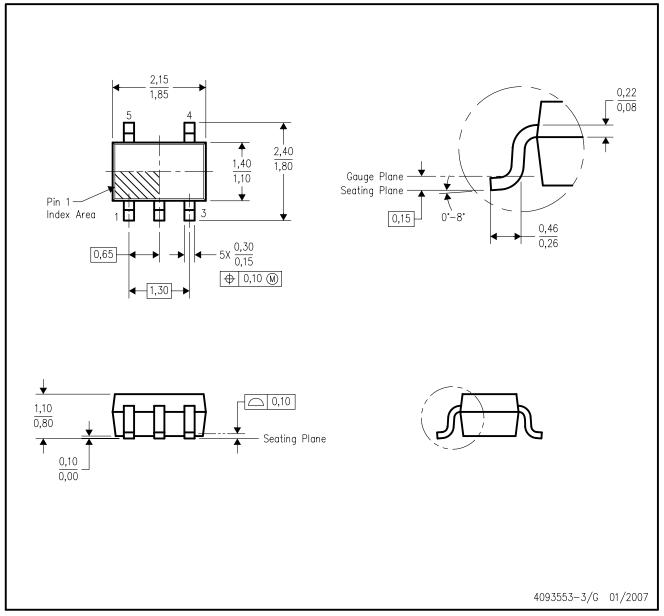

DBV (R-PDSO-G5)

## PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-178 Variation AA.

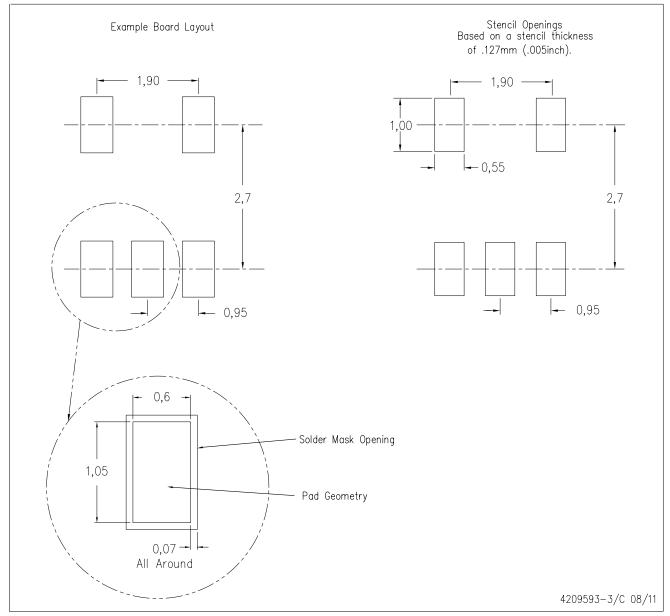

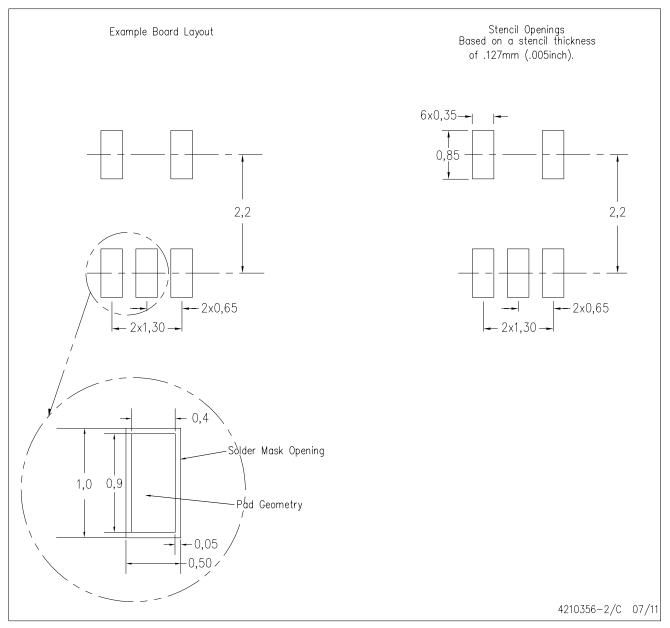

# DBV (R-PDSO-G5)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

# DCK (R-PDSO-G5)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- D. Falls within JEDEC MO-203 variation AA.

# DCK (R-PDSO-G5)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

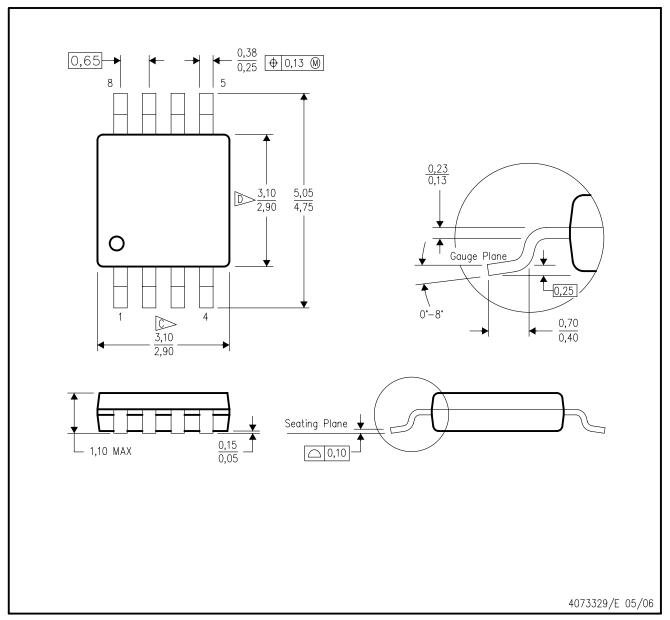

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

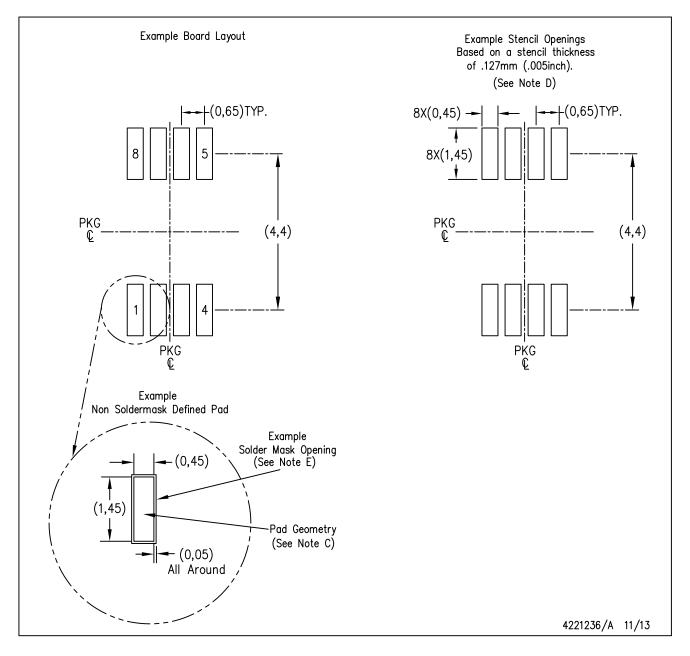

# DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PW (R-PDSO-G14)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

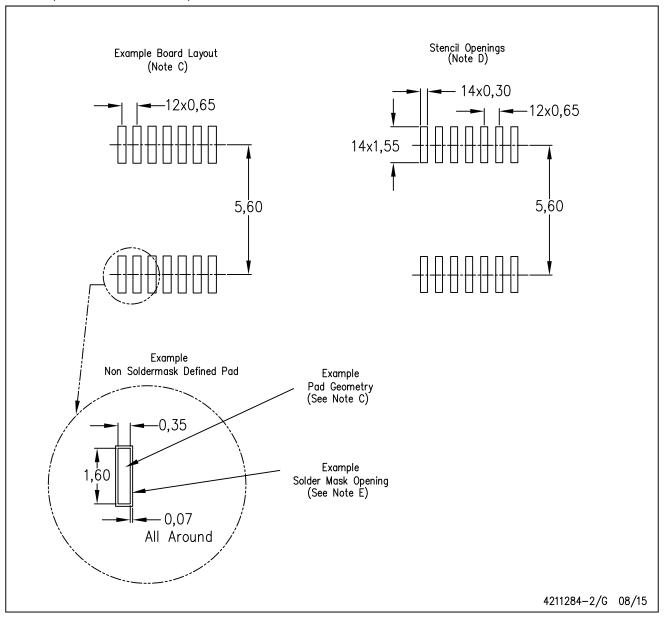

# PW (R-PDSO-G14)

# PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

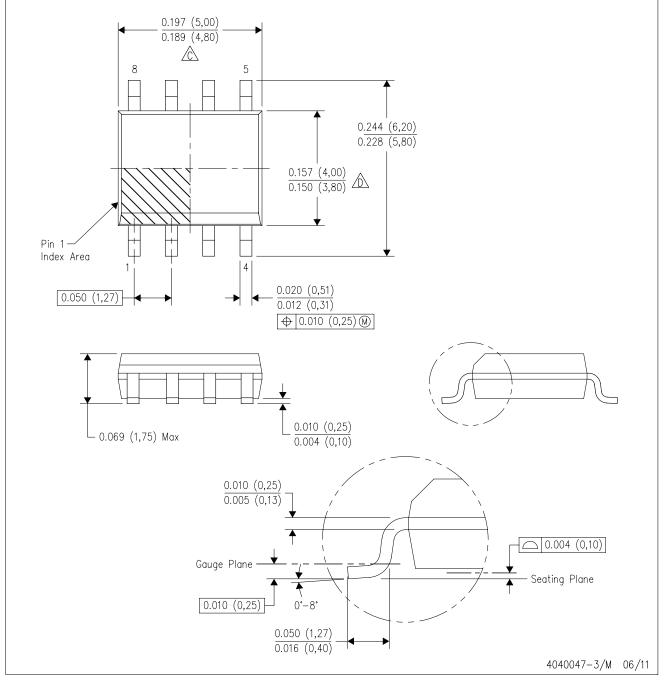

# D (R-PDSO-G8)

## PLASTIC SMALL OUTLINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

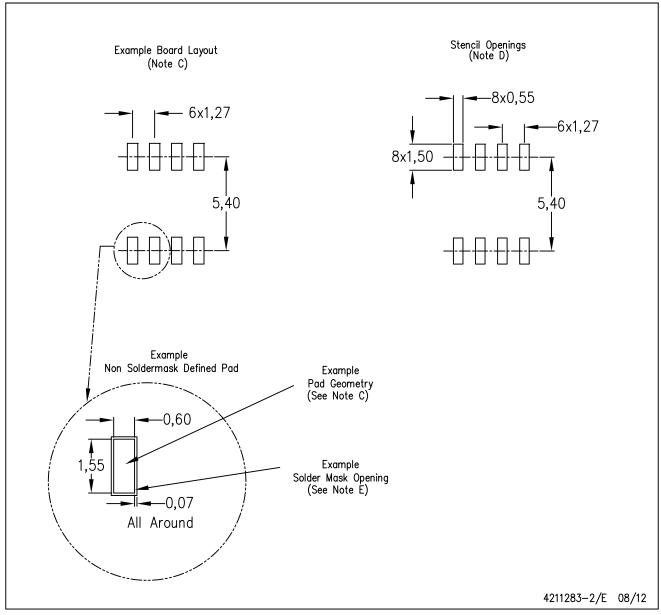

# D (R-PDSO-G8)

# PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### 重要声明

德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行 复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III (或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

|               |                                    |              |                          |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated